Tuning Image And Sensor Systems To Military Functions Using FPGAs

By Brian Durwood, Ed Trexel, and Ross Snider

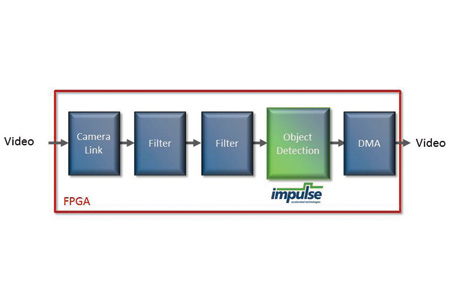

The use of high-level language (HLL) techniques makes it easier to tune FPGAs for specific projects.

Several trends at the "bleeding edge" of image and sensor processing are leading software developers to consider offloading compute-bound processes to field-programmable gate arrays (FPGAs). FPGAs are, admittedly, a bit harder to work with and certainly more expensive than CPUs or GPUs. So, what makes them worthwhile? A few things:

Several trends at the "bleeding edge" of image and sensor processing are leading software developers to consider offloading compute-bound processes to field-programmable gate arrays (FPGAs). FPGAs are, admittedly, a bit harder to work with and certainly more expensive than CPUs or GPUs. So, what makes them worthwhile? A few things:

Foremost, users have the ability to architect (or "tune") the majority of the FPGA logic primarily toward the specific process being accelerated. Second, users can combine all functions on a single device (a system-on-chip, or SoC). Third, users can reduce power by extensive parallelization of processes to run at slower clock speeds and at lower equivalent power. Finally, FPGA processing time can be deterministically counted in clock cycles, as compared to the indeterminate behavior of operating systems.

Get unlimited access to:

Enter your credentials below to log in. Not yet a member of Photonics Online? Subscribe today.